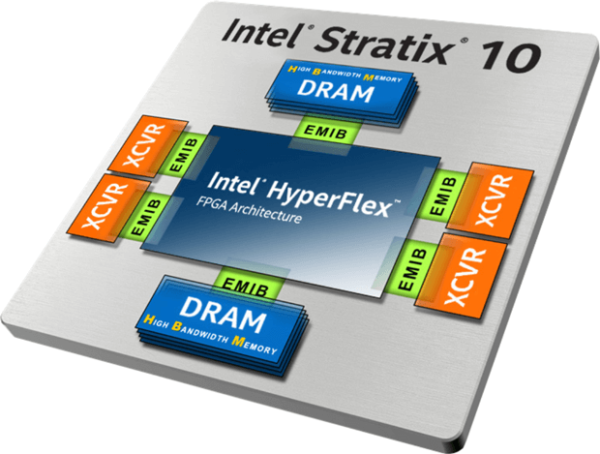

在板載二代高頻寬記憶體(HBM 2)、以及尚未正式宣佈聯姻的 Intel CPU 和 Radeon GPU 的基礎上,Intel將使用 EMIB 來掛接Stratix 10 MX FPGA 晶片,最多四塊“瓷貼”可提供高達 512GB/s 的頻寬。

除了 HBM2 記憶體堆疊,Intel還會使用 EMIB 掛接四個 FPGA 信號收發器,比如 PCIe 。在白皮書(PDF)中,Intel還提到了使用 FPGA 和 DDR4 記憶體來擴展當前系統級架構所面臨的挑戰。

三通道 DDR4-3200 記憶體或許可以滿足當前 FPGA 的 80 Gb/s 頻寬需求,但縮放比例和佈局上的挑戰,在當今的架構中幾乎是不可能克服的。

隨著未來 FGPA 處理需求的增長,無法無限地在一片基板上安裝足夠多的 DDR I/O 針腳來滿足其頻寬需求。

即便有可能在 FGPA 封裝包上安置足夠多的 I/O 針腳,額外的每條記憶體也需要佔用相當耗能的 I/O 緩衝來驅動它們,導致頻寬的需求超出了對每瓦特性能尤為敏感的資料中心等市場的設計限制。

最後,Intel指出,將 10 組 DDR4 DIMM 插槽放到一塊 PCB 上,理論上可達 256GB/s 吞吐率(在未來對 FPGA 也有這方面的某些需求),但會佔用相當多的面積、讓資料中心的密度不增反減。

上面提到的許多限制,也是 AMD 開始開發 HBM 記憶體來滿足其 GPU 頻寬需求的一個主要原因。與佔用大量 PCB 面積的 GDDR5 顯存晶片相比,HBM 不僅占地更小,所需佈置的線路和能耗也更少。

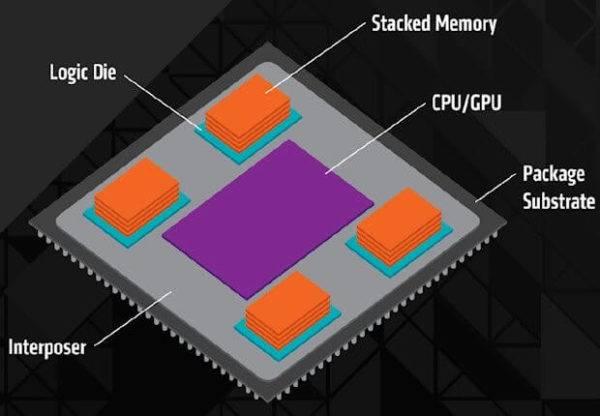

目前廠商們多需要在 GPU 和 HBM 顯存之間使用仲介層(interposer),這顆額外的矽晶片確實也很佔位置,不僅增加了封裝的複雜性,也限制了晶片整體尺寸的收縮。

因此,Intel對 EMIB 的定位是‘克服使用 DDR4 和 FPGA 以增加頻寬的挑戰’。

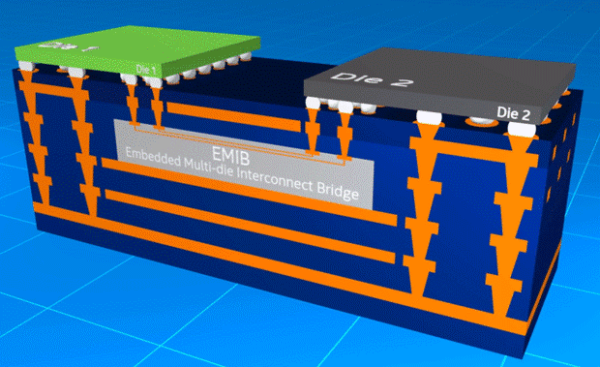

與 Fuji 和 Vega GPU 上的 HBM 顯存所搭檔的仲介層不同,EMIB 讓Intel的 Stratix 10 MX FPGA 在納入 HMB2 顯存時的占地限制沒那麼大。

Intel表示,使用 EMIB 還可以讓那些類似的基板受益,因為橋接器只是很小的一片,採用微凸(micro-bumps)而不是矽通孔(TSVs)來連接核心。

此外該公司不用擔心製造上的挑戰、或者減少 TSV 的產量,因為它可以使用標準的倒裝晶片技術,封裝集合成 EMIB 的晶片。

最終,所有這些奇特的技術,都可以讓 Stratix 10 MX FPGA 晶片盡享指數級的記憶體頻寬增長。

與目前 FPGA 方案相比(4~6 組 DDR 通道),其支援多達 64 組的併發記憶體訪問。

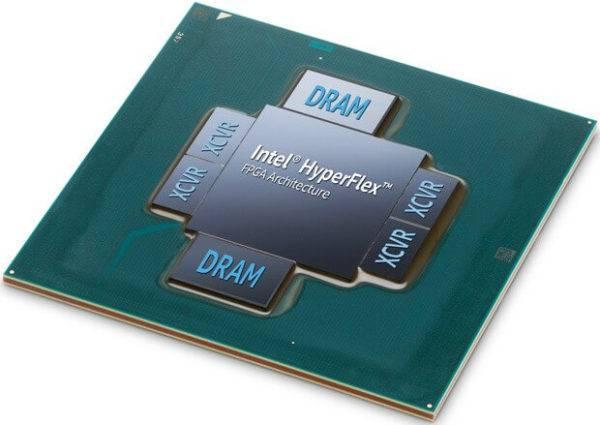

另外,該 FPGA 晶片採用Intel的 HyperFlex 架構打造,運行頻率可以達到 1GHz 。隨著後續的優化,其能夠達到更高的性能和應用加速的靈活性。

資料來源

沒有留言:

張貼留言