採用7nm Zen 2架構的AMD產品家族的布局接近圓滿,其於市場上亦取得不俗反饋。

現在,經玩家挖掘,Ryzen處理器內核的更多技術細節曝光在大家面前。

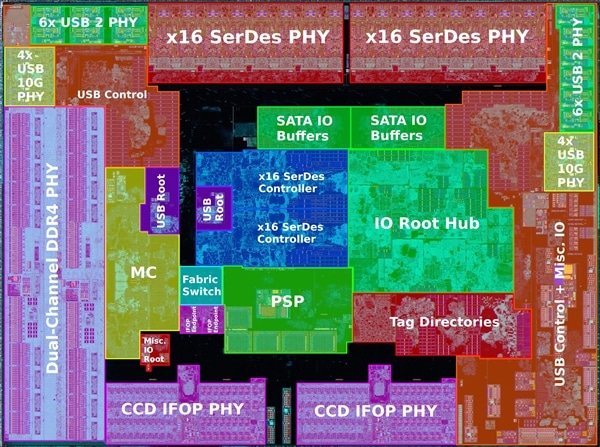

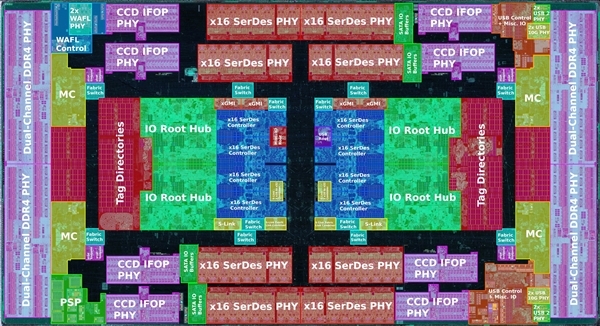

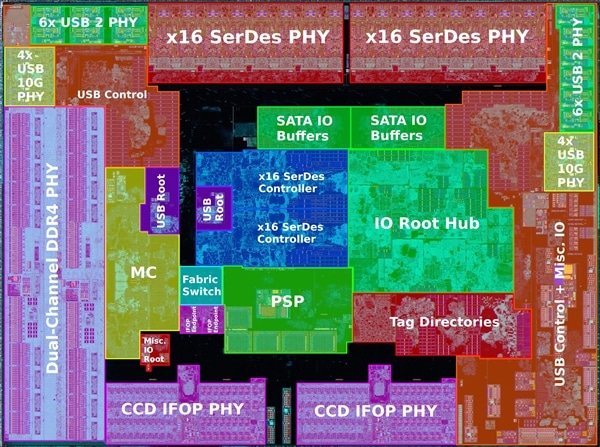

基於Fitzchens Fitz的裸片透視,工程師Nemez用彩圖的形式將”Matisse”(對應Ryzen 3000處理器)及”Rome”(對應第二代EPYC)中IO晶片的”五臟六腑”給標記了出來。

簡單解釋一下,Ryzen 3000處理器、第二代EPYC採取的都是CCD+I/O Die的封裝方式,一個CCD對應8核心Zen 2,而I/O裸片採用14nm製程打造,CCD的結構AMD官方有公布,此處繪製的是I/O Die。

以”Matisse”為例,I/O裸片中擁有兩個x16 SerDes主控(可同時管理PCIe、SATA、USB 3等介面)、一個I/O根核心、兩個x16 SerDes物理層等。

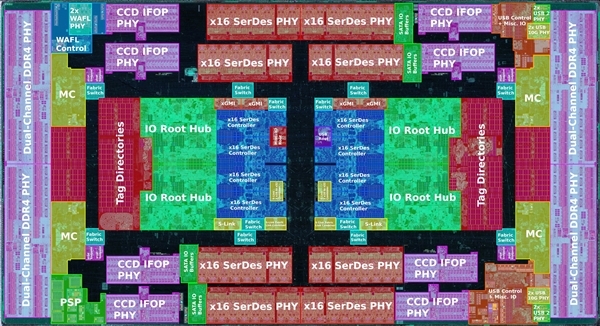

對比”Rome”,x16 SerDes主控多達八個,而三代Ryzen Threadripper(Castle Peak)則遮蔽了其中四個,對於玩家來說,此即為三代Threadripper限制為四通道記憶體的根本原因。

訊息來源

現在,經玩家挖掘,Ryzen處理器內核的更多技術細節曝光在大家面前。

基於Fitzchens Fitz的裸片透視,工程師Nemez用彩圖的形式將”Matisse”(對應Ryzen 3000處理器)及”Rome”(對應第二代EPYC)中IO晶片的”五臟六腑”給標記了出來。

簡單解釋一下,Ryzen 3000處理器、第二代EPYC採取的都是CCD+I/O Die的封裝方式,一個CCD對應8核心Zen 2,而I/O裸片採用14nm製程打造,CCD的結構AMD官方有公布,此處繪製的是I/O Die。

以”Matisse”為例,I/O裸片中擁有兩個x16 SerDes主控(可同時管理PCIe、SATA、USB 3等介面)、一個I/O根核心、兩個x16 SerDes物理層等。

對比”Rome”,x16 SerDes主控多達八個,而三代Ryzen Threadripper(Castle Peak)則遮蔽了其中四個,對於玩家來說,此即為三代Threadripper限制為四通道記憶體的根本原因。

訊息來源

沒有留言:

張貼留言