在昨天AMD隆重推出其3D V-Cache Design之後,AMD已確認該技術將在明年初推出的Zen3的Ryzen CPU中導入。

AMD在解釋這項技術方面做得很好,但沒有說明哪些Zen CPU將率先採用該技術。他們的展示包括採用Zen3的Ryzen 9 5900X原型,該公司現已確認3D V-Cache晶片堆疊技術確實首先應用於Zen3 CPU。

AMD提供了更多細節,確認該技術將用於Zen3的CPU,更具體地說是Ryzen CPU。CPU將在今年晚些時候生產,因此我們可以期待在2022年初會推出。

距離AMD轉換到Zen4還有至少兩個季的時間。但AMD沒有說明這些是桌上型還是行動處理器會採用,但從外觀上看桌上型Ryzen CPU更有可能發生。AMD將專注於代號為 Rembrandt的下一代Ryzen APU,據傳將採用新的Zen3+核心,而Ryzen桌上型CPU將重用現有的Zen3核心並增加3D V-Cache。

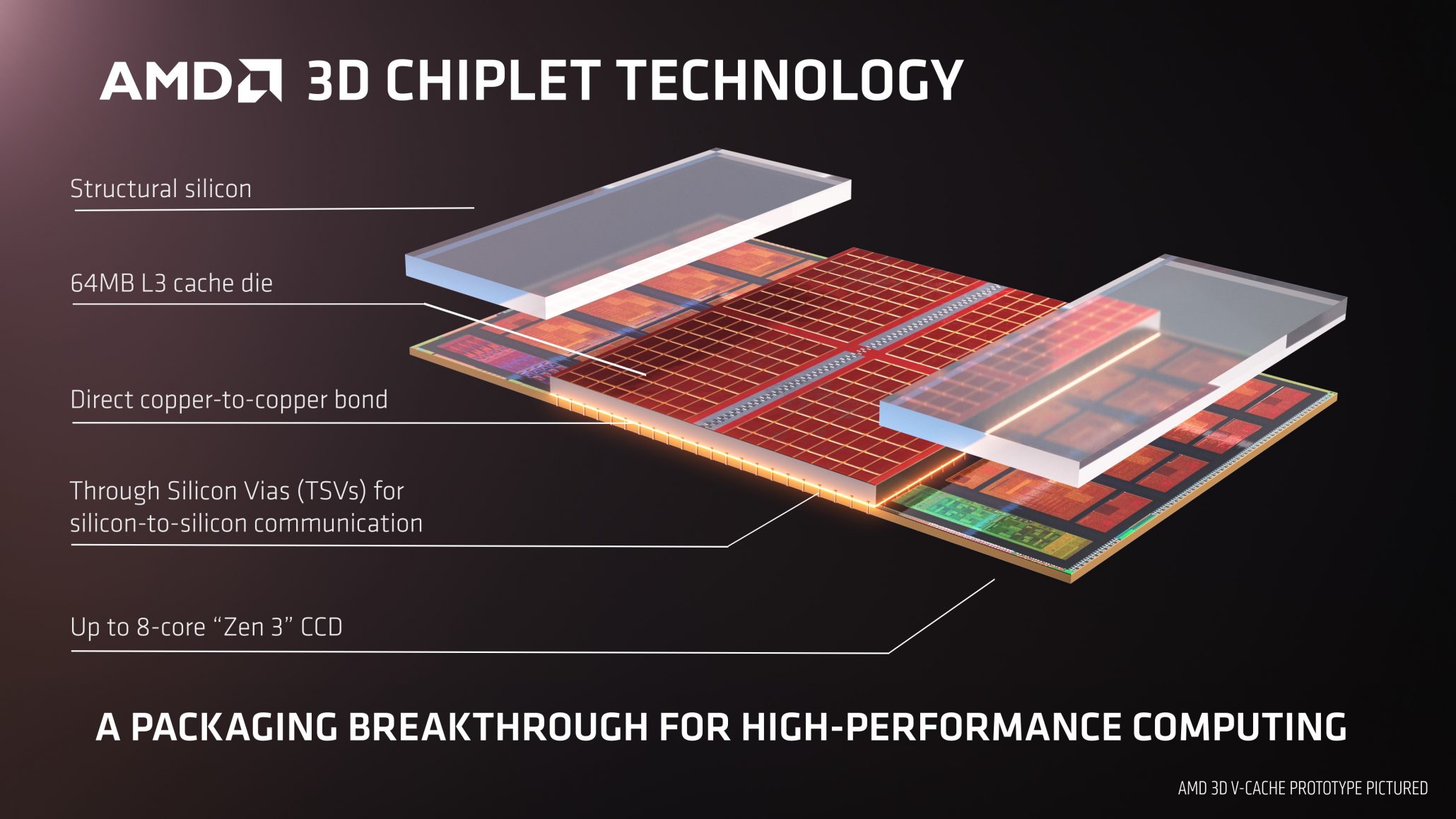

單3D V-Cache堆棧包含64MB的L3快取,使用在現有Zen3 CCD之上。快取將增加在增加現有的32MB L3 ,每個CCD總共有96MB。所以將包括每個小晶片1個3D V-Cache堆棧,因此我們可以看到頂級Ryzen SKU上總共會有192MB的快取。但是AMD表示V-Cache堆棧可以達到8-hi,這意味著除了每個Zen3 CCD 的32MB快取之外,單個CCD在技術上還可以提供高達512MB的L3。

AMD已經精簡了Zen3 CCD和V-Cache,因此它們的高度與當前的Zen3處理器相同,而不是核心和IOD之間的高度不同。由於V-Cach位於CCD L3快取的頂部,因此它不會影響核心的熱量輸出。

AMD還展示了其採用小晶片架構CPU的下一代3D堆疊設計。該技術預計將多個IP堆疊在一起,但AMD展示的原型包括帶有3D V-Cache和64MB L3 SRAM的 Ryzen 9 5900X。

該原型擁有一個標準Zen3 CCD,旁邊是一個3D封裝的CCD,其尺寸為6mmx6mm (36mm2)。CCD的大小與以前相同,但在CCD之上還有另一個封裝,它有64 MB快取,增加了Zen3 CCD上已有的32MB L3快取。

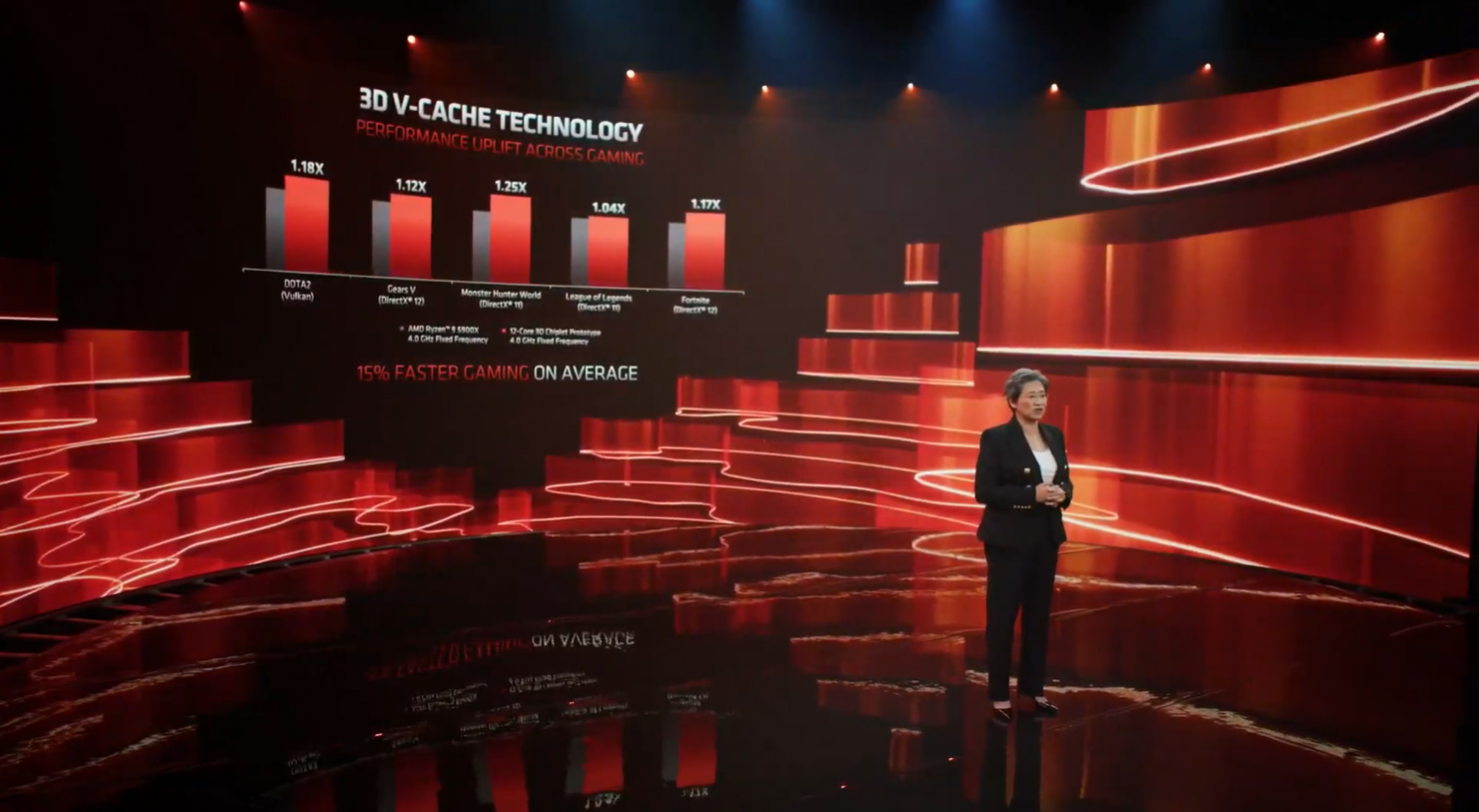

AMD甚至展示了這個原型,這意味著該技術確實有效,而不僅僅是紙上展示。Ryzen 9 5900X原型執行Gears V,由於增加了遊戲快取大小,性能提高了12%。平均而言AMD聲稱透過3D V-Cache設計提高了15%的性能。每個V-Cache堆棧提供高達2TB/s的總頻寬。

沒有留言:

張貼留言